FPGA-MPC

FPGA-Accelerated ADMM Solver for Convex Model Predictive Control

Embedded Systems Design (CSEE 4840) @ Columbia University

Team: Alexander Du, Apurva Reddy, Roy Hwang, Godwill Agbehonou

FPGA-MPC is a hardware-accelerated solver for Model Predictive Control (MPC) implemented on an Intel Cyclone V FPGA (DE1-SoC). The project accelerates the Alternating Direction Method of Multipliers (ADMM) algorithm, inspired by TinyMPC, to solve trajectory optimization problems in real-time.

The system features a custom SystemVerilog implementation of the ADMM solver using fixed-point arithmetic, a Linux device driver for memory-mapped communication, and a Python-based UDP simulator for validating the control logic with a simulated Crazyflie quadrotor.

System Architecture

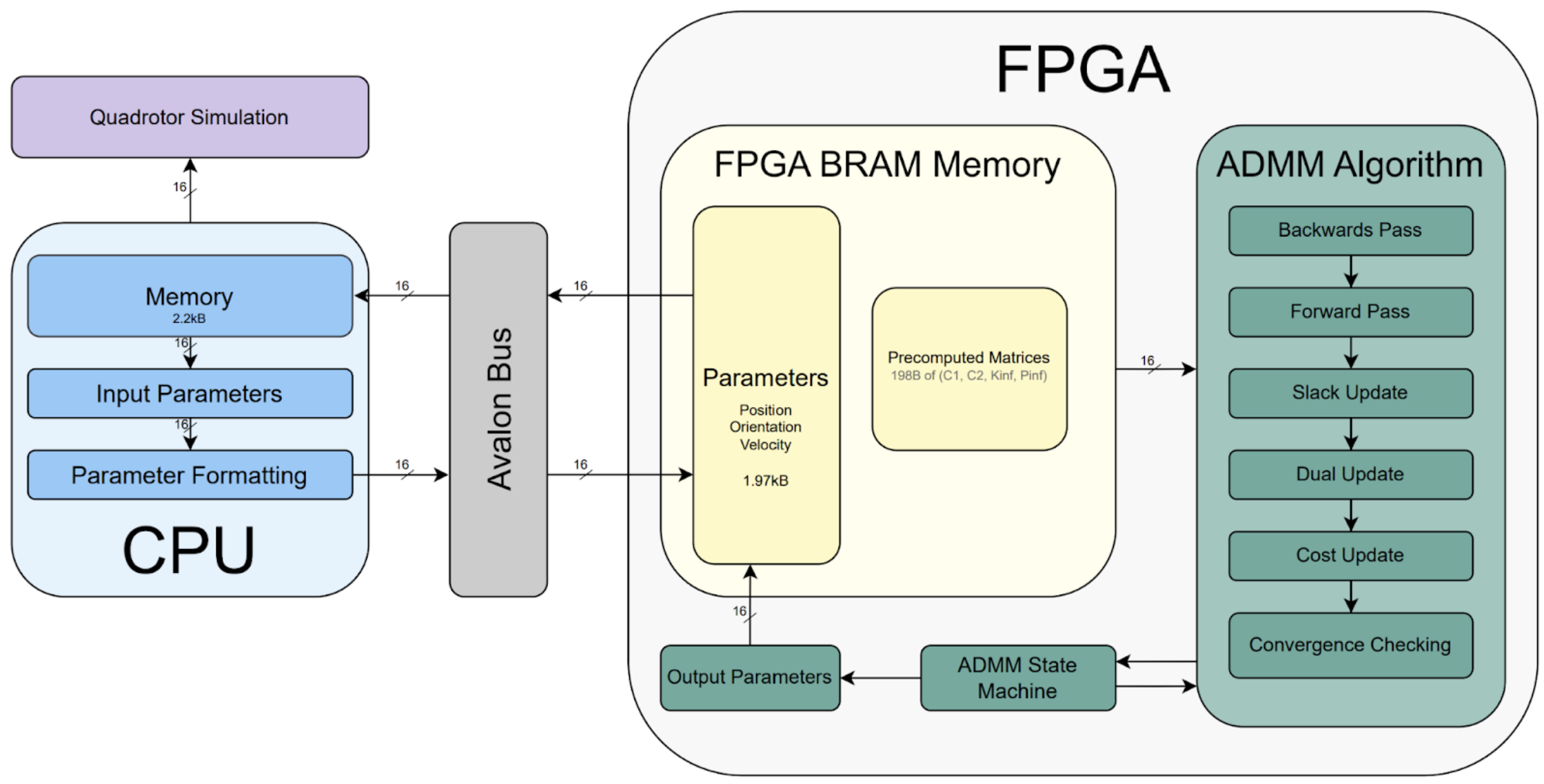

Dataflow diagram showing the interaction between the Quadrotor Simulator, HPS (CPU), and FPGA Fabric.

Technical Implementation

Hardware (SystemVerilog)

- Fixed-point arithmetic implementation of ADMM

- Custom memory interface via Avalon Bus

- Parallelized primal, slack, and dual updates

- Pipelined residual calculation

Software (C/Linux)

- Memory-mapped interface driver

- Linux userspace application for solver control

- Network interface for external simulation

Simulation (Python)

- UDP-based quadrotor simulator

- Real-time visualization of trajectory tracking

- Integration with hardware-in-the-loop setup